”数字IC 总结“ 的搜索结果

2022届数字IC秋招个人总结

【酒酒】数字IC手撕代码总结,1. 用任意语言写1:100的质数(7.17) 2 2. 奇数分频(三分频)(7.18) 3 3. 偶数分频(二分频)(7.19) 5 4. 画出可以检测10110串的状态转移图,要求每检测到一次该序列,输出两个...

01前言本人研究生就读于某985大学,集成电路工程专业,成绩中上,研究方向是基于新型存储器件的非易失性逻辑设计(其实就是将新型的器件(RRAM和FeRAM)和电路结合起来)更加偏向于模拟...

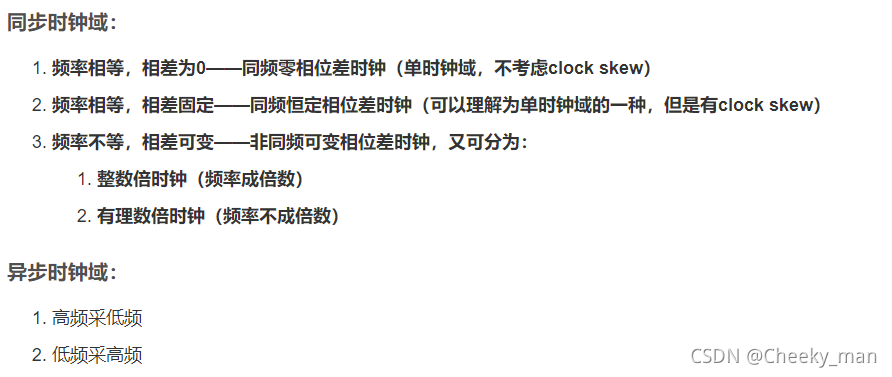

讲了同步异步,时序设计,FPGA内部资源分析,时钟和复位,状态机,数电知识,信号处理知识,PFGA设计优化等等,前面列列举的只是一小部分。

数字IC设计的过程总结

标签: 范文/模板/素材

数字IC设计的过程总结,包含基础的IC设计的流程,职业规划,全面的介绍了芯片设计的全过程。

3、经典DC综合中文总结pdf: 高级ASIC芯片综合 4、经典STA静态时序分析pdf: Static Timing Analysis for Nanometer Designs 5、CMOS VLSI Design A Circuits and Systems Perspecctive 6、硬件架构的艺术【英】

文档内总结了FPGA开发工程师、数字IC设计工程师等相关岗位面试时会被问到的基础题,亲测有效可参考

2021年数字IC秋招总结 到今天为止从4月开始的秋招正式结束 教育背景:本科双非,硕士南航 offer情况:联芸科技,瑞晟微电子,华为,沛睿微电子,全志科技 秋招心得 1.尽早地投递简历,数字IC这个行业越来越火热,也...

数字ic设计_总结复习

标签: 面试

数字IC低功耗设计综述

标签: 数字IC功耗

数字IC的低功耗设计是一个系统问题,必须在设计的各个层次上发展适当的技术,综合应用不同的设计策略,才 能达到在降低功耗的同时还能维持较高的系统性能的目的。本文系统地总结了当前系统级芯片设计中的低功耗技术...

本文总结了模拟IC与数字IC的区别。

23届数字IC验证秋招总结

标签: 前端

数字IC前端面试问题总结

标签: 面试

数字IC验证虚拟项目总结

标签: 面试

数字IC设计笔试面试经典题

标签: 数字IC设计

数字IC设计笔试面试经典题目总结与答案详细分析,内容丰富,有33页的题目总结

数字IC与模拟IC到底哪个更适合你?

主要考虑有涵盖硬件,FPGA/数字IC,嵌入式软件,机器学习。 1.1 硬件开发设计 1.2 嵌入式软件方面 1.3 FPGA/数字IC 2、行业选择的定位 2020年9月26日记录:以下仅为本人秋招的一点感悟,作为个人记录分享。 ...

文章目录 文章目录0. 前言 如果正准备入行数字芯片设计行业可以看看下几篇行业入门介绍的文章,因水平有限,文中难免存在疏漏、错误之处,与最新技术脱节之处必定不少,敬请细心的读者不吝指教。...数字IC设计入门篇

数字IC笔试面试常考问题及答案

标签: IC

文章目录引言1、准备入门IC的全局观念系列1.1 [准备入门IC的全局观念系列-上](https://blog.csdn.net/ciscomonkey/article/details/103717582)1.2 [准备入门IC的全局观念系列-中]...

数字IC设计的一些英语术语总结(持续更新。。。) AXI (Advanced eXtensible Interface ) AMBA (Advanced Microcontroller Bus Architecture) DMA(Direct Memory Acess) FPGA (Filed Programmble Gate Array) ...

数字IC面经汇总(32篇)

标签: fpga开发

为准备校招(自用),博主整理了往年数字IC前端(设计&&验证) && FPGA的面经,信息来自但不限于数字IC打工人、FPGA探索者、摸鱼范式、CSDN、牛客网、博客园等公众号和网站,以及博主个人的面试经验。内容来源较多,...

推荐文章

- php 上传图片 缩略图,PHP 图片上传类 缩略图-程序员宅基地

- scrapy爬虫框架_3.6.1 scrapy 的版本-程序员宅基地

- 微信支付——统一下单——java_小程序统一下单接口-程序员宅基地

- (已解决)报错 ValueError: Tensor conversion requested dtype float32 for Tensor with dtype resource-程序员宅基地

- 记录el-table树形数据,默认展开折叠按钮失效_eltable一刷新展开的子节点展开按钮消失-程序员宅基地

- 设计模式复习-桥接模式_csdn天使也掉毛-程序员宅基地

- CodeForces - 894A-QAQ(思维)_"qaq\" is a word to denote an expression of crying-程序员宅基地

- java毕业生设计移动学习网站计算机源码+系统+mysql+调试部署+lw-程序员宅基地

- 14种神笔记方法,只需选择1招,让你的学习和工作效率提高100倍!_1秒笔记 高级-程序员宅基地

- 最新java毕业论文英文参考文献_计算机毕业论文javaweb英文文献-程序员宅基地